300 mmウエハーの共用パイロットラインで新規装置・材料の技術検証が可能に

ポイント

・ 独自技術で構成された、最先端半導体製造装置を有する共用パイロットラインを国内で初めて構築

共用可能なプロセスで、最先端ロジック半導体で使用されるゲートオールアラウンド(GAA)構造

・ トランジスタの試作が可能に

・ 共用パイロットラインを国内の企業・大学などに提供し、最先端の技術開発を支援

概 要

国立研究開発法人 産業技術総合研究所 (以下「産総研」という) 先端半導体研究センターは、NEDO(国立研究開発法人 新エネルギー・産業技術総合開発機構)助成事業の元、国内半導体製造装置メーカー3社(東京エレクトロン株式会社、株式会社SCREENセミコンダクターソリューションズ、キヤノン株式会社)との共同研究を通じ、最先端ロジック半導体で使用されるゲートオールアラウンド(GAA)構造のトランジスタを独自技術に基づき実現するとともに、企業などが利用可能な共用パイロットラインを国内で初めて確立しました。本パイロットラインは、半導体装置・材料メーカーなどが、300 mmシリコンウエハー上に最先端トランジスタ構造を試作し、技術の検証を行える国内唯一の共用パイロットラインであるという点が大きな特色です。すなわち、国内半導体製造装置メーカーや関連材料メーカーが自社で開発した装置や材料を一連の製造工程内に適用することで、最先端トランジスタ製造工程への適合性の検証を行うことが可能となります。先端半導体デバイスに係る半導体基礎科学の深堀りや新構造・新機能材料の組み合わせによる次世代半導体技術の創造を通じて、国内半導体関連企業や大学の研究開発を加速させ、特に大きな海外シェアを有している国内半導体製造装置メーカー、半導体材料メーカーの国際競争力の強化と若手の人材育成につなげます。

この成果の詳細は、2025年11月14日に産総研先端半導体研究センター第二回公開シンポジウム(富士ソフトアキバプラザ アキバホール)において発表されます。

下線部は【用語解説】参照

社会的背景

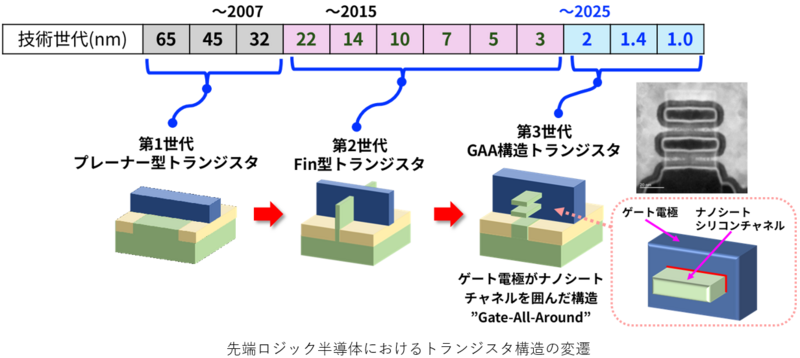

AI技術の高度化が進み、先端ロジック半導体への性能向上要求が継続しています。これに応えるため、集積回路を構成するトランジスタの微細化、高密度集積化が進んでいます。ロジック半導体チップ向けトランジスタは、先端半導体で主流な構造として使用されているFin型構造から、多段の極薄膜シリコンチャネル(シリコンナノシート)をゲートで包むGAA構造への移行が進んでおり、海外半導体メーカーにおいて製品への搭載が本格化しつつあります。このような複雑な立体構造を持つトランジスタの実現には、従来に増して高度なプロセス技術が要求されます。日本の半導体製造装置メーカーや半導体材料メーカーは高い国際競争力を有しており、先端半導体のサプライチェーンの中でも重要な役割を果たしています。しかし、単一企業だけでトランジスタを試作し自社で開発した技術の検証を行うことは、設備投資の負担やトランジスタ製造工程の複雑化によりきわめて困難になっています。また、現在量産されている先端半導体は300 mmウエハーによる製造工程により生産されるため、実用化するプロセス技術は300 mmウエハーに対応する試作設備において開発・試験を行う必要があります。これまで国内にはこのような試作検証が可能な設備がなく、海外機関の試作設備を使用する場合には、ノウハウを含む知財などの機微情報に海外機関が関わらざるを得ないという状況でした。

開発の経緯

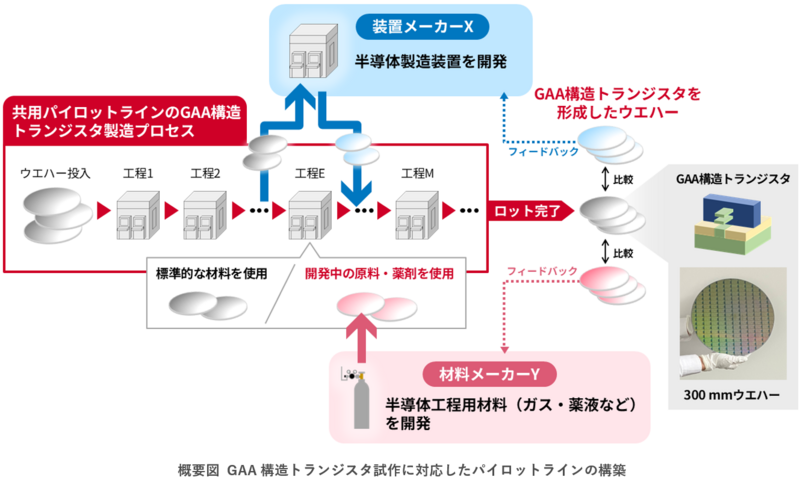

産総研先端半導体研究センターでは、NEDO助成事業である「ポスト5G情報通信システム基盤強化研究開発事業」における「先端半導体の前工程技術(More Moore技術)の開発」(2021~2025年度、実施機関:東京エレクトロン株式会社、株式会社SCREENセミコンダクターソリューションズ、キヤノン株式会社)に対応した共同研究として、「先端3次元構造ロジック半導体デバイスの製造・プロセス技術の開発と検証用パイロットライン整備」を推進しています。この事業の中で、企業などが活用可能な産総研スーパークリーンルームに新規に16台の最先端装置を導入し、300 mmウエハーに対応した共用パイロットライン (以下「300 mmパイロットライン」という)の構築を進めてきました(概要図)。

研究の内容

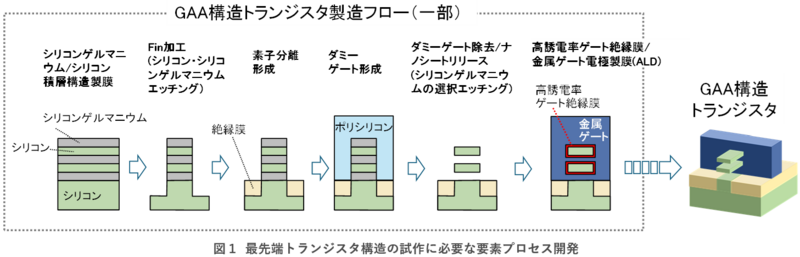

産総研スーパークリーンルームの300 mmパイロットラインに、産総研が設計した性能仕様に基づき最先端半導体製造装置を新規に導入、それぞれのプロセスレシピを開発し、GAA構造トランジスタの試作に必要な要素プロセスを確立しました。具体的には、多段シリコンナノシートを形成するシリコン・シリコンゲルマニウム結晶膜成膜技術、シリコンナノシート層のみを残してシリコンゲルマニウム層を選択エッチングする技術、シリコンナノシートを囲むゲート絶縁膜とゲート金属電極を堆積させる成膜技術、トランジスタのしきい値を制御するためのゲート絶縁膜厚と金属膜厚を精密に調整する原子層堆積(ALD)技術などが必須であり、産総研スーパークリーンルームにおいてこれらのプロセスを新たに開発しました(図1)。すべての要素プロセスは、NEDO事業を共同で実施する半導体製造装置メーカー3社と個別に連携して開発し、特に、GAA構造トランジスタ形成の主要工程となる、シリコン・シリコンゲルマニウムエッチング工程、高誘電率ゲート絶縁膜・金属ゲート電極構造の形成工程は、各社から産総研への人材の派遣も含め、それぞれ密接な連携の元、開発を進めました。開発したプロセスはプロセスモジュールとして活用できる形で整備し、すべてのプロセスは産総研が適切にノウハウ管理し、パイロットラインを利用する企業などが制約なく最先端トランジスタ構造を試作し、技術の検証ができるようにしています。また、本パイロットラインではGAA構造トランジスタの試作だけでなく、その基盤となるFin型トランジスタなど、プロセスモジュールを活用できる他の試作実証も可能です。

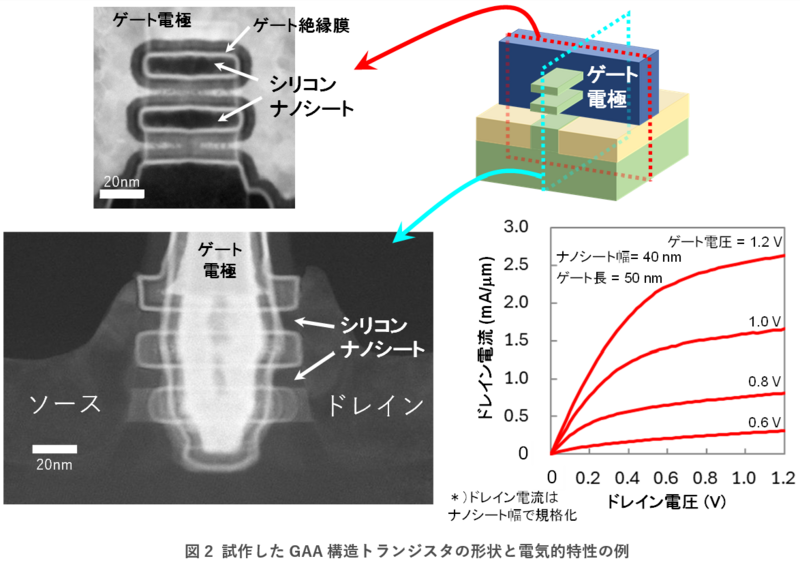

GAA構造トランジスタの試作に必要な要素プロセスを統合し、一連の製造工程を実施して試作を行い、その動作を確認しました(図2)。ゲート電極の断面電子顕微鏡写真よりシリコンナノシートの周りをゲート絶縁膜とゲート電極が取り囲んでいる形状が、ソース・チャネル・ドレインを横切る断面電子顕微鏡写真よりシリコンナノシートがソース・ドレイン電極に正しく接続されていることが確認できます。また電気特性評価の結果、ゲート電圧の印加によりドレイン電流がon-off制御される正常な電流電圧特性が得られていることを確認しました。

なお以上の成果は、NEDOの助成事業「ポスト5G情報通信システム基盤強化研究開発事業」(JPNP20017)により得られたものです。

波及効果

産総研が確立した標準的なトランジスタ試作条件をもとに、国内企業や大学などが独自のプロセス技術開発を行い本パイロットラインにおける試作を実施することにより、独自プロセスを適用した最先端トランジスタ構造の性能面での良否を評価することが可能となります(概要図)。例えば、半導体製造装置メーカーにおいては、自社で開発中のプロセス装置により一連のトランジスタ製造工程の一部を実施することで、半導体関連材料メーカーにおいては自社で開発した材料を一連のトランジスタ製造工程の一部に適用することで、最先端トランジスタ製造工程への適合性の検証を行うことが可能となります。また本パイロットラインでは、試作プロセスの提供のみならず、試作したトランジスタの電気的評価、プロセス途中の各種物理分析手法も提供可能です。国内企業が海外機関の試作設備を利用する場合、海外機関および海外企業が、国内企業のノウハウや知財などに関わらざるを得ない状況となっています。産総研ではこれまでに「先端半導体製造技術コンソーシアム」を設立し、本コンソーシアムにおいてパイロットラインの利用に係るノウハウなどの共用知財の取り扱いルールを整備しました。本コンソーシアムにはすでに5法人がライン利用を目的に入会しており、これら国内企業や大学などが本パイロットラインを活用して国内で機微な技術の研究開発を行うことができるようになります。本事業を共同で実施した装置メーカー3社によるパイロットライン活用もすでに進んでいます。また、パイロットラインを活用する企業・大学などの研究者や技術者が産総研スーパークリーンルームで活動することで、先端半導体製造技術に係る若手人材育成にもつなげます。

世界の半導体産業の市場規模は、半導体製造装置で2024年に1169億ドルと前年比10.5 %の成長、半導体材料で2024年に675億ドルと前年比3.8 %の成長となっており、規模も大きく成長を続けています。経済産業省の「半導体・デジタル産業戦略」において、先端半導体の製造装置・材料のサプライチェーンを強化する方針が明記されており、世界シェア約3割を有する国内半導体製造装置メーカー、世界シェア約5割を有する国内半導体材料メーカーの国際競争力を維持・強化するうえで本パイロットラインは重要な役割を果たします。

今後の予定

今後は、ゲート電極の寸法の微細化、ならびに、nチャネル型トランジスタとpチャネル型トランジスタの両方を実現するCMOS化など、要素プロセスの高度化と拡充を進め、トランジスタ性能や信頼性の向上、また低消費電力化に資する技術の創出を目指します。また、300 mmパイロットラインを利用した企業などとの共同研究を推進し、本成果の普及を進めていきます。さらに、将来世代の新構造・新材料デバイスの試作や高周波アナログ素子開発、新材料チャネル・多機能デバイスを搭載した回路試作なども可能なプラットフォームへの拡張を目指します。

用語解説

ロジック半導体

集積回路用半導体デバイスは主に「ロジック演算用」と「メモリ用」に分類される。スマートフォンやパソコン、サーバーに搭載され、電子機器の制御やデータ処理の役割を担う、演算用半導体素子。

ゲートオールアラウンド(GAA)構造トランジスタ

トランジスタ構造の一つ。チャネル(電流が流れる部位)の上下左右の4面すべてをゲート電極で覆うことで、トランジスタを微細化した際に漏れ電流を抑えつつ高速に動作できるようにした構造。トランジスタの微細化に伴う高性能化と低消費電力化の両立のため、2 nm世代より最先端集積回路に本格的に導入される。

パイロットライン

量産の前段階で、新しい材料や工法の生産を試験的に行うための小規模の生産ライン。先端半導体では300 mmシリコンウエハーを扱うラインが必要であり、産総研では300 mmウエハーに対応したスーパークリーンルームに構築を進めている。

Fin型構造

ロジック半導体向けトランジスタは、十数年前までは、シリコン基板表面をチャネルとする平面構造だったが、微細化に伴いシリコン基板を垂直に加工し形成した薄いチャネルをゲート (電流を制御する部位) で挟むFin型に移行し、これが現在でも先端半導体として主流な構造となっている。

シリコンナノシート

トランジスタにおいて電流のオン・オフをつかさどるチャネル構造の一種。GAA構造トランジスタで使用され、半導体をナノメートルレベルの厚さの二次元的なシート状に加工したもの。

シリコン・シリコンゲルマニウム結晶膜成膜技術

単結晶であるシリコン基板上に、下地の結晶と整合した欠陥のない結晶薄膜を成膜する技術。GAA構造において最終的にチャネルとして使用するシリコンナノシート層とその間の犠牲層となるシリコンゲルマニウム層を、欠陥のない単結晶膜として成膜することが、GAA構造トランジスタの製造に必要不可欠である。

原子層堆積(ALD)

原料ガスの対象構造への吸着と、膜の材料を合成するための化学反応を1原子層ごとに繰り返す成膜方法。1 nm以下の膜厚の制御性と、GAA構造のようなナノシート間の隙間や側壁にも均一に成膜できる特徴があり、GAA構造トランジスタの製造に必要不可欠である。

シリコン・シリコンゲルマニウムエッチング工程

3次元的な立体構造を有するGAA構造トランジスタでは、形状を定義するエッチング工程の高度化が非常に重要となっている。シリコン・シリコンゲルマニウムの積層膜からFin構造に垂直に加工する工程は深さ方向に削る異方性が重要であり、一方でシリコン・シリコンゲルマニウムの積層構造Finからシリコンゲルマニウム層を除去する工程では、Fin側壁方向からのエッチングを可能とする等方性とシリコンゲルマニウムのみ削る材料選択性が重要である。

高誘電率ゲート絶縁膜

ゲート絶縁膜の誘電率を高めることで膜厚を薄くすることと等価の性能向上効果を得る技術。技術世代が進むにつれてトランジスタのゲート絶縁膜を薄くする必要があり、本技術は、プレーナー型トランジスタの最終世代において導入された。最先端のGAA型では、このゲート絶縁膜をナノシート間の隙間にも均一に成膜する必要があり、原子層堆積(ALD)技術が成膜に使用される。

先端半導体製造技術コンソーシアム

本パイロットラインの円滑な運営と開発された技術の普及を目的として2020年に産総研が設立したコンソーシアム。本コンソーシアムにおいてパイロットラインで利用できるノウハウなどの共用知財の取り扱いルールを整備し、本コンソーシアムに企業、大学などが入会することでパイロットラインを活用できることとしている(https://unit.aist.go.jp/cpo-eleman2022/ASMA/)。

半導体・デジタル産業戦略

経済産業省がまとめた半導体やデータ産業などのデジタル産業支援についての政策指針。半導体製造装置・材料産業のサプライチェーン強化についても明記されている。

出典:https://www.meti.go.jp/policy/mono_info_service/joho/conference/semiconductors_and_digital.pdf

CMOS

Complementary Metal Oxide Semiconductor(相補型金属酸化膜半導体)の略で、p型デバイスとn型デバイスを組み合わせた電子回路。片方がオン状態の時、他方がオフ状態となる相補的な動作をする。低消費電力、回路構成が簡素になる、など多くの利点がある。

プレスリリースURL

https://www.aist.go.jp/aist_j/press_release/pr2025/pr20251105/pr20251105.html